Difference between revisions of "Fitlet1 FACET Cards"

(→FACET Card Mechanical Interface) (change visibility) |

|||

| Line 197: | Line 197: | ||

''FACET LAN DXF file'' | ''FACET LAN DXF file'' | ||

[[File:FACET_LAN_DXF_file.png]] | [[File:FACET_LAN_DXF_file.png]] | ||

| + | |||

FACET PCB design should meet mini PCI Express design guidelines in terms of edge connector design (hard gold fingers), PCB thickness, other parameters, and follow general recommendations described in PCI express mini card electromechanical specification 1.2. | FACET PCB design should meet mini PCI Express design guidelines in terms of edge connector design (hard gold fingers), PCB thickness, other parameters, and follow general recommendations described in PCI express mini card electromechanical specification 1.2. | ||

Revision as of 08:14, 9 September 2015

Concept

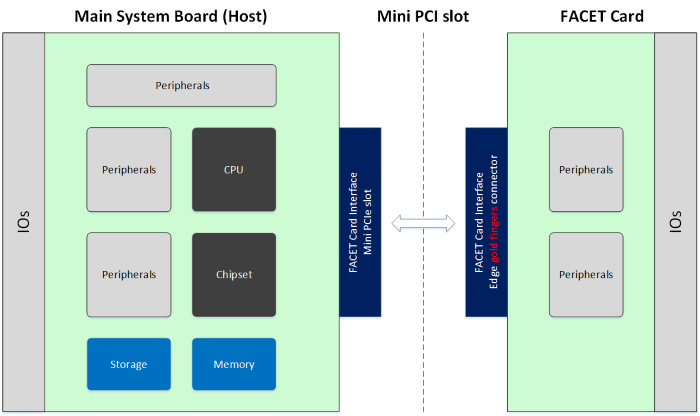

FACET Cards are implemented with internal T-shaped extension board. The extension board is connected to already available motherboard’s mini PCI Express slot, featuring standard PC interfaces such as PCIe, USB2, SMBus and LPC Bus.

FACET Card Electrical Interface

FACET Card interface based on regular mini PCI Express interface featuring extended signals and functionality, as legacy LPC Bus interface and additional PCI Express lanes.

fitlet mini PCI Express edge connector pinout

| fitlet mini PCI Express edge connector | |||||

|---|---|---|---|---|---|

| Pin # | Pin Name | Signal Description | Pin # | Pin Name | Signal Description |

| 1 | WAKE# | Open drain, active low signal driven low by a mini PCIe card to reactivate the PCIe link | 2 | 3.3Vaux | 3.3V power rail |

| 3 | PERn2 | PCI Express Gen2 differential receive pair 2 | 4 | GND | Ground connection |

| 5 | PERp2 | 6 | 1.5V | 1.5V power rail | |

| 7 | CLKREQ# | Clock request - open drain, active low driven by mini PCIe card to request PCIe reference clock | 8 | LAD0 | LPC Bus Data signals |

| 9 | GND | Ground connection | 10 | LAD1 | |

| 11 | REFCLK- | Reference clock used to assist the synchronization of PCI Express interface timing circuits | 12 | LAD2 | |

| 13 | REFCLK+ | 14 | LAD3 | ||

| 15 | GND | Ground connection | 16 | LFRAME# | LPC Bus frame signal. Active Low |

| Mechanical Notch Key | |||||

| 17 | PETn2 | PCI Express Gen2 differential receive pair 2 | 18 | GND | Ground connection |

| 19 | PETp2 | 20 | W_DISABLE# | Active low signal when asserted by the system disable radio operation. Reserved for future use. | |

| 21 | GND | Ground connection | 22 | PERST# | Asserted when power is switched off and also can be used by the system to force HW reset |

| 23 | PERn0 | PCI Express differential receive pair | 24 | 3.3Vaux | 3.3V power rail |

| 25 | PERp0 | 26 | GND | Ground connection | |

| 27 | GND | Ground connection | 28 | 1.5V | 1.5V power rail |

| 29 | GND | Ground connection | 30 | SMB_CLK | Optional SMBus two-wire interface for Host/mini PCIe module communication |

| 31 | PETn0 | PCI Express differential transmit pair | 32 | SMB_DATA | |

| 33 | PETp0 | 34 | GND | Ground connection | |

| 35 | GND | Ground connection | 36 | USB_D- | USB Host Interface |

| 37 | LPC_CLK0 | LPC Bus clock | 38 | USB_D+ | |

| 39 | 3.3Vaux | 3.3V power rail | 40 | GND | Ground connection |

| 41 | 3.3Vaux | 3.3V power rail | 42 | LED_WWAN# / LPC_SMI# | Active low output signals are provided to allow status indications to users via system provided LEDs (or LPC Bus control signals) |

| 43 | PETn1 | PCI Express Gen2 differential transmit pair 1 | 44 | LED_WLAN# / LPC_PME# | |

| 45 | PETp1 | 46 | LED_WPAN# / SERIRQ | ||

| 47 | LPC_RST# | LPC Bus Reset signal. Active Low | 48 | 1.5V | 1.5V power rail |

| 49 | PERn1 | PCI Express Gen2 differential receive pair 1 | 50 | GND | Ground connection |

| 51 | PERp1 | 52 | 3.3Vaux | 3.3V power rail | |

FACET Card Mechanical Interface

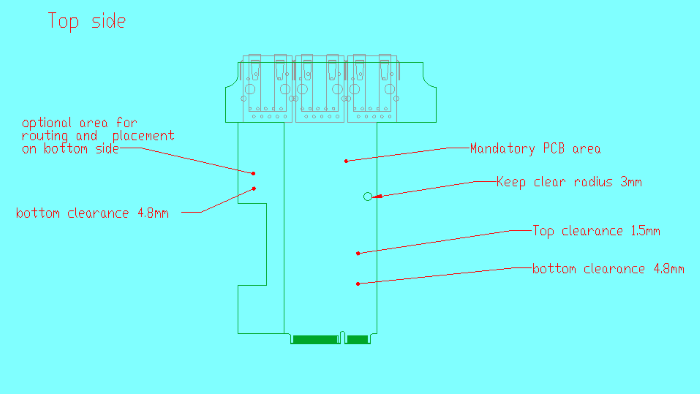

As noted in the previous section, FACET interface based on standard mini PCI express connection, electrical as well as mechanical, meaning all mechanical and layout guidelines apply for FACET mechanical design. PCB shape of custom FACET derived from fitlet-X PCB design, mechanical stack-up and other mechanical constraints, shown in the DXF file below. The file can be downloaded from product wiki portal.

FACET PCB design should meet mini PCI Express design guidelines in terms of edge connector design (hard gold fingers), PCB thickness, other parameters, and follow general recommendations described in PCI express mini card electromechanical specification 1.2.